Top 10 Semiconductor Design Tools: The EDA Software Powering Modern Chips

From Cadence to Synopsys, discover the essential EDA tools that enable engineers to design everything from smartphone processors to AI accelerators. Explore the $15 billion software ecosystem behind every modern chip.

Behind every smartphone processor, graphics card, and AI accelerator lies a sophisticated ecosystem of Electronic Design Automation (EDA) tools. These software platforms enable engineers to design, simulate, and verify chips containing billions of transistors—a task impossible without advanced computational assistance.

The EDA industry, worth over $15 billion annually, is dominated by a handful of specialized companies whose tools are essential for modern semiconductor design. Let's explore the top 10 tools that power the chip industry.

The EDA Industry Leaders

Synopsys

Market LeaderMarket Share: ~35%

Revenue: $5.8B (2024)

Speciality: Logic synthesis, verification

Key Tools: Design Compiler, VCS, PrimeTime

Customers: Apple, Intel, Samsung, TSMC

Cadence

Strong #2Market Share: ~30%

Revenue: $4.1B (2024)

Speciality: Analog/mixed-signal, layout

Key Tools: Virtuoso, Innovus, Spectre

Customers: Qualcomm, Broadcom, MediaTek

Siemens EDA (Mentor Graphics)

SpecializedMarket Share: ~15%

Revenue: $1.2B (2024)

Speciality: PCB design, automotive

Key Tools: Calibre, HyperLynx, Tessent

Customers: BMW, Ford, Bosch, NXP

Top 10 Semiconductor Design Tools

Synopsys Design Compiler

Logic Synthesis

Company

Synopsys

Primary Use

RTL to gate-level synthesis

Market Position

Industry Standard

The gold standard for converting RTL code into optimized gate-level netlists. Used in 90%+ of digital chip designs worldwide.

Cadence Virtuoso

Analog/Mixed-Signal Design

Company

Cadence

Primary Use

Analog circuit design & layout

Market Position

Analog Leader

The dominant platform for analog and mixed-signal design, essential for RF chips, power management, and high-speed interfaces.

Synopsys VCS

Simulation & Verification

Company

Synopsys

Primary Use

RTL simulation & debug

Market Position

Verification Standard

High-performance simulator for verifying digital designs, supporting SystemVerilog and UVM methodologies.

Cadence Innovus

Physical Design

Company

Cadence

Primary Use

Place & route, timing closure

Market Position

P&R Leader

Advanced place-and-route tool for complex SoC designs, optimizing for power, performance, and area.

Siemens Calibre

Physical Verification

Company

Siemens EDA

Primary Use

DRC, LVS, parasitic extraction

Market Position

Verification Standard

The industry standard for physical verification, ensuring designs meet foundry manufacturing rules.

Synopsys PrimeTime

Static Timing Analysis

Gold standard for timing verification and optimization

Cadence Spectre

Analog Simulation

High-accuracy SPICE simulator for analog circuits

Synopsys IC Compiler

Physical Design

Comprehensive P&R solution for advanced nodes

Cadence Genus

Logic Synthesis

Advanced synthesis with machine learning optimization

Ansys HFSS

Electromagnetic Simulation

3D electromagnetic field simulation for RF/mmWave

The Semiconductor Design Flow

From Concept to Silicon

Specification & Architecture

Define requirements, create system architecture, and plan implementation strategy.

RTL Design & Coding

Write HDL code (Verilog/VHDL) describing the digital logic functionality.

Verification & Simulation

Test the design using simulators and formal verification tools.

Logic Synthesis

Convert RTL to gate-level netlist using synthesis tools.

Physical Design

Place and route the design, optimize for timing, power, and area.

Physical Verification

Check design rules, layout vs. schematic, and extract parasitics.

How to Choose the Right EDA Tools

Key Selection Factors

Design Complexity

Match tool capabilities to your design requirements

Technology Node

Ensure tools support your target manufacturing process

Team Expertise

Consider learning curve and available training

Integration Requirements

Tool compatibility and data exchange formats

Cost Considerations

License Models

• Node-locked: $50K-500K per seat

• Floating: 20-30% premium

• Cloud-based: Usage-based pricing

Hidden Costs

• Training and support: 15-25% of license

• Compute infrastructure: $100K-1M+

• Annual maintenance: 18-22% of license

The Future of EDA: AI and Machine Learning

AI-Powered Design Optimization

Modern EDA tools are incorporating machine learning to automate complex optimization tasks that traditionally required expert knowledge and manual tuning.

Synthesis

AI-driven logic optimization and technology mapping

Place & Route

ML-based congestion prediction and routing optimization

Verification

Automated test generation and coverage analysis

Emerging Trends

- • Cloud-native EDA platforms

- • AI-assisted design space exploration

- • Automated analog circuit synthesis

- • Real-time design optimization

- • Predictive yield analysis

Challenges

- • Model training data quality

- • Interpretability of AI decisions

- • Integration with legacy flows

- • Computational resource requirements

- • IP protection and security

Validating EDA Tool Results

EDA tools are only as good as their validation. Design teams must verify that tool outputs meet specifications and perform correctly in silicon.

Common Validation Challenges:

- • Tool correlation across different vendors

- • Model accuracy vs. silicon results

- • Corner case coverage verification

- • Process variation impact analysis

- • Cross-domain validation (analog/digital)

Best Practices:

- • Multi-tool verification flows

- • Silicon correlation studies

- • Automated regression testing

- • Comprehensive design rule checking

- • Post-silicon validation feedback

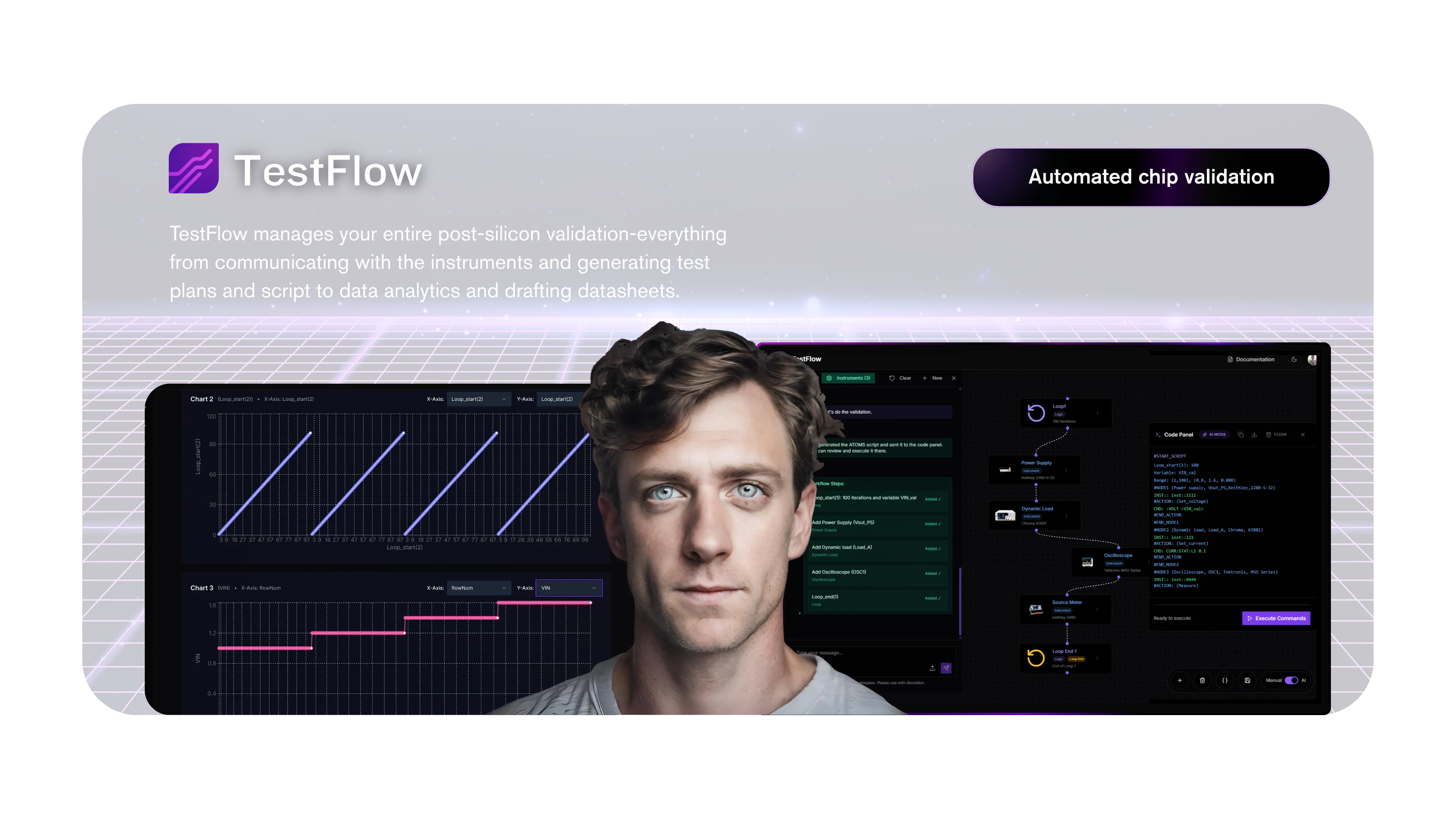

TestFlow for EDA Tool Validation

Modern validation platforms like TestFlow complement EDA tools by providing comprehensive post-design verification, ensuring that synthesized and implemented designs meet all performance, power, and reliability requirements.

Learn More About Design ValidationThe EDA Ecosystem Continues to Evolve

The semiconductor design tools landscape is rapidly evolving, driven by increasing design complexity, advanced manufacturing processes, and the integration of AI/ML technologies. While established players like Synopsys, Cadence, and Siemens EDA continue to dominate, new entrants are bringing fresh approaches to long-standing challenges.

Success in semiconductor design increasingly depends not just on having the right tools, but on how effectively teams can integrate, validate, and optimize their design flows. The future belongs to companies that can seamlessly combine traditional EDA excellence with modern AI-powered optimization and validation techniques.

As chips become more complex and design cycles compress, the role of sophisticated EDA tools becomes even more critical. Understanding and mastering these tools is essential for any team serious about competing in the modern semiconductor industry.

Optimize Your Design Validation Process

While EDA tools handle design and synthesis, comprehensive validation ensures your chips work correctly in real-world conditions. TestFlow's AI-powered platform complements your EDA flow with advanced testing and verification capabilities.