In semiconductors, timing is everything. A 6-month delay isn't just a schedule slip—it can be a $100 million mistake that reshapes competitive positioning for years. With design windows growing tighter, development costs soaring, and market opportunities becoming more fleeting, time-to-market has become the ultimate competitive differentiator in the chip industry.

Why Time-to-Market Pressure is Brutal in Semiconductors

The semiconductor industry operates under unique pressures that make timing more critical than in virtually any other sector. Understanding these dynamics is essential for anyone working in chip design, validation, or manufacturing.

Design Windows Are Tight

Consumer electronics, data centers, automotive, and telecom all operate on synchronized product cycles. Miss the window, and your chip might get skipped for an entire generation of devices. OEMs plan their product roadmaps years in advance, and late silicon can derail entire product launches.

Critical Windows

- • Consumer electronics: Annual cycles

- • Automotive: 3-5 year design cycles

- • Data center: 18-24 month refresh

- • Mobile: Bi-annual flagship launches

Consequences of Missing

- • Design win loss to competitors

- • Reduced product lifecycle

- • Lower pricing power

- • Market share erosion

High Fixed Costs, Delayed Revenue

Chip development requires massive upfront investments—$50M to $500M+ for advanced processors. These costs accumulate regardless of when the chip ships, but revenue only begins after successful market launch. Every month of delay burns cash while competitors potentially capture market share.

First-to-Silicon Advantage

In the semiconductor industry, the first working silicon often wins the socket. While competitors are still debugging their designs in simulation or struggling with first silicon bring-up, the early mover is already engaging with customers, securing design wins, and locking in contracts for high-volume production.

The Hidden Costs of Semiconductor Delays

Beyond the obvious revenue impact, semiconductor delays create cascading effects that can damage long-term competitive positioning and customer relationships.

| Delay Impact | Immediate Effect | Long-term Consequence | Typical Cost |

|---|---|---|---|

| Customer Penalties | Contract penalties, lost bonuses | Damaged customer relationships | $5-50M per customer |

| Opportunity Cost | Missed design wins | Competitor entrenchment | $50-200M in lifetime revenue |

| Resource Burn | Extended engineering costs | Delayed next-gen development | $10-30M per quarter |

| Node Transition | Reduced peak value window | Technology obsolescence | 20-40% revenue reduction |

"In semiconductor manufacturing, time-to-market is not just a metric—it's the difference between market leadership and perpetual catch-up. A 6-month delay in silicon isn't just a schedule slip—it can be a $100M+ mistake."

The Validation Bottleneck: Where Time Gets Lost

While chip design complexity continues to grow, validation has emerged as the primary bottleneck in semiconductor development cycles. Post-silicon validation now consumes 50% or more of total development time, making it the critical path for time-to-market optimization.

Validation Timeline Breakdown

How validation phases consume development time in modern semiconductor projects

Pre-Silicon Validation

Simulation, emulation, and design verification before chip fabrication. Critical for catching design errors early, but limited in scope compared to real silicon testing.

Post-Silicon Bring-Up

Getting first silicon to boot and run basic functions. Often reveals issues that simulations missed, requiring multiple debug and optimization cycles.

Performance Optimization

Tuning chip performance to meet specifications, optimizing power consumption, and validating across all operating conditions and use cases.

Production Validation

Final validation for manufacturing release, including reliability testing, compliance verification, and customer qualification.

Case Study: The Cost of Validation Delays

Consider a real-world scenario: a leading semiconductor company developing a next-generation AI accelerator for data center applications. Their experience illustrates the brutal economics of time-to-market in modern chip development.

AI Accelerator Development Timeline

Original Plan

- • Total development: 24 months

- • Validation phase: 8 months

- • Target market entry: Q1 2024

- • Projected first-year revenue: $200M

- • Development investment: $300M

Actual Reality

- • Total development: 30 months (+25%)

- • Validation phase: 14 months (+75%)

- • Actual market entry: Q3 2024

- • Actual first-year revenue: $120M (-40%)

- • Total investment: $380M (+27%)

Financial Impact

The 6-month delay cost approximately $150M in lost revenue opportunity, $80M in additional development costs, and enabled a competitor to capture significant market share with an earlier product launch.

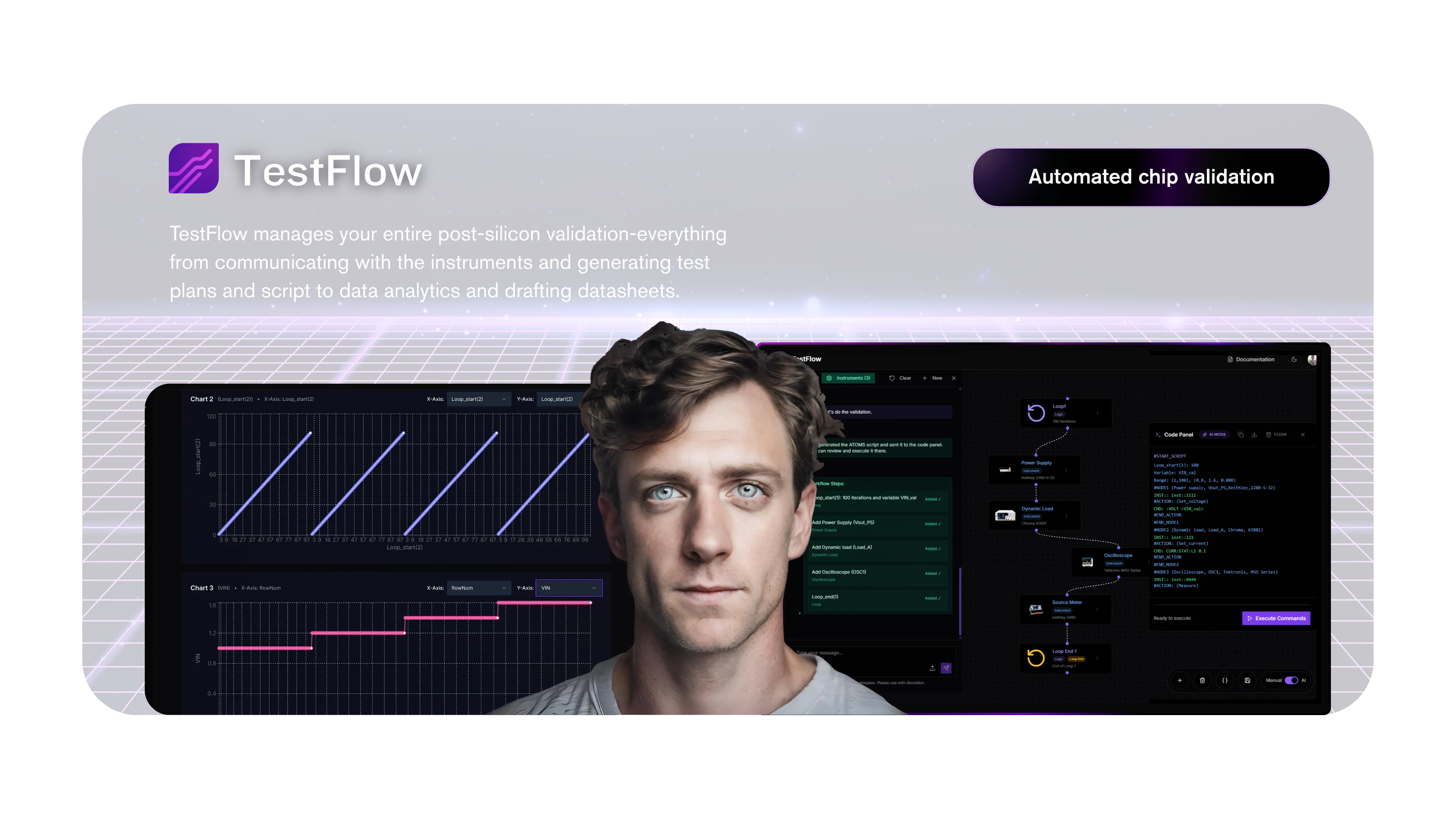

The Modern Solution: AI-Powered Validation

Forward-thinking semiconductor companies are addressing time-to-market challenges by revolutionizing their validation approaches. AI-powered platforms like TestFlow are transforming how teams approach post-silicon validation, dramatically reducing cycle times while improving coverage and reliability.

TestFlow: Accelerating Time-to-Market

AI-powered automation reduces validation cycles from months to weeks while improving test coverage and reliability

Traditional Validation Challenges

- • Manual test case creation (weeks of effort)

- • Sequential debugging and optimization

- • Limited test coverage due to time constraints

- • Reactive problem-solving approaches

- • Resource-intensive validation teams

- • Inconsistent testing methodologies

TestFlow AI-Powered Solutions

- • Automated test generation (hours vs. weeks)

- • Parallel testing and optimization

- • Comprehensive coverage through AI analysis

- • Predictive issue identification

- • Streamlined validation workflows

- • Consistent, repeatable methodologies

Quantifying the Time-to-Market Impact

Companies implementing modern validation approaches are achieving dramatic improvements in time-to-market while maintaining or improving product quality. Here's what industry leaders are reporting:

Validation Speed

70%

Reduction in validation cycle time using AI-powered automation platforms

Coverage Improvement

45%

Increase in test coverage achieved through intelligent test generation and optimization

Cost Savings

60%

Reduction in validation resource requirements through automation and optimization

Industry Examples: Winners and Losers in Time-to-Market

The semiconductor industry provides numerous examples of how time-to-market performance directly translates to business success or failure.

Success Stories

NVIDIA H100 Launch

NVIDIA's rapid H100 validation and launch captured the AI training market before competitors, establishing a dominant position worth hundreds of billions in market value.

Apple M1 Transition

Apple's efficient M1 validation enabled a smooth transition from Intel, capturing performance leadership and improving margins simultaneously.

Cautionary Tales

Intel 10nm Delays

Years of 10nm process delays allowed AMD to capture significant CPU market share and enabled TSMC to establish leadership in advanced node manufacturing.

Various Mobile Processor Delays

Several mobile processor companies have lost major design wins due to validation delays, allowing competitors to capture flagship smartphone sockets.

TestFlow: Transforming Validation Speed

At Atoms, we're directly addressing the validation bottleneck that's slowing semiconductor time-to-market. TestFlow's AI-powered platform automates the most time-consuming aspects of post-silicon validation while improving coverage and reliability.

How TestFlow Accelerates Time-to-Market

Automated Test Generation

AI algorithms analyze chip specifications and automatically generate comprehensive test suites, eliminating weeks of manual test development while improving coverage.

Intelligent Debug Acceleration

Machine learning models analyze test failures and automatically suggest root causes, reducing debug time from weeks to days for complex issues.

Parallel Validation Workflows

Cloud-native architecture enables massive parallel testing, running thousands of validation scenarios simultaneously rather than sequentially.

Predictive Issue Detection

AI-powered analysis identifies potential problems before they become critical issues, enabling proactive optimization rather than reactive debugging.

Real-World Results: Companies Accelerating with TestFlow

Leading semiconductor companies implementing TestFlow are achieving remarkable improvements in their time-to-market performance:

Major CPU Manufacturer

Reduced post-silicon validation from 16 weeks to 4 weeks for their next-generation server processor, enabling them to capture early data center design wins.

AI Chip Startup

Achieved first-pass silicon success with comprehensive validation completed in 6 weeks, enabling rapid customer engagement and securing Series B funding.

"TestFlow's AI-powered validation platform has completely transformed our time-to-market performance. We went from 20-week validation cycles to 6 weeks, while actually improving our test coverage. This technology has given us a significant competitive advantage."

Strategic Recommendations: Optimizing Time-to-Market

Based on analysis of successful semiconductor companies and time-to-market best practices, here are key recommendations for optimizing development cycles:

Time-to-Market Optimization Framework

- Invest in Validation Automation: AI-powered platforms can reduce validation time by 60-80% while improving coverage

- Implement Parallel Development: Overlap design, validation, and production planning phases rather than sequential execution

- Focus on First-Pass Success: Invest in pre-silicon validation to minimize post-silicon debug cycles

- Establish Clear Milestones: Create accountability and visibility into validation progress with measurable checkpoints

- Build Validation Expertise: Develop internal capabilities in modern validation methodologies and tools

The Future of Semiconductor Time-to-Market

As chip complexity continues to increase and market demands intensify, time-to-market will become even more critical. Companies that master rapid validation and deployment will dominate their markets, while those clinging to traditional approaches will struggle to compete.

The semiconductor industry is entering an era where validation speed determines market success. AI-powered platforms like TestFlow represent the future of chip validation—enabling companies to move from silicon to market faster than ever before while maintaining the reliability and performance that customers demand.

Accelerate Your Time-to-Market with TestFlow

Don't let validation delays cost you millions in lost opportunities. TestFlow's AI-powered platform helps semiconductor companies reduce validation cycles by up to 70% while improving coverage and reliability. Join the companies that are winning through faster time-to-market.